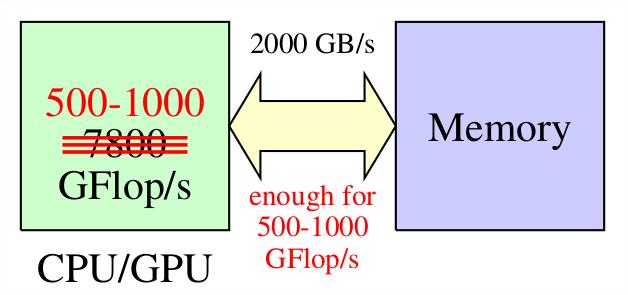

It is clear that the memory bandwidth is the key parameter that, together with the arithmetic intensity, determines the actual computing power of a processor solving a simulation problem.

If, e.g., the memory bandwidth is increased to 2000 GB/s, we can expect that the actual performance of a single processor could optimally be from 500 GFlop/s (the extreme case of the HPCG benchmark) up to about 1000 GFlop/s for general simulations.

The present LOWAIN consortium has no skills and equipment to design an accelerators with high memory bandwidth, but preliminary contacts with a global company that masters the necessary technology has been started.